Mail:info@anke-pcb.com

WhatApp / Wickat: 008618589033832

Skype: Sannyduckp

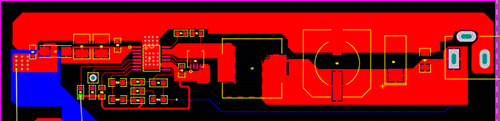

Dräi Aspekter fir Kraaft Integritéit ze sécherenPCB Designing

De modernsten engem modoriséiert engem elektronesche Design, ass d'Kraaft Integritéit am PCB d'Design vum PCB Design. Fir déi stabil opfirfirmierksam ze suergen, datt déi exklusiv Operatioun vun elektronesch Applia sech ugesinn an designt mat der Kraaftwierker beim Verschmolfung zu engem Empfängeren.

Duerch virsiichteg virzestellen an d'Muechtmoduler, banneschten Layer Fligeren, a Power Versuergungs Chips kënne mir wierklech Kraaft Integritéit erreechen. Dësen Artikel schleeft dës dräi Schlësselspaart fir praktesch Féierung a Strategien ze bidden fir PCB Designer.

I. Power Modul Layout Wiring

Du, steet d'Energiequell vun all elektronesch Normiséierung, déi eng Stabilitéit an d'Intemizienz vu de ganze System akzeptéiert. De richtege Layout a Routing kann net nëmmen Nimm Interferenz reduzéieren awer och glat aktuelle Stroum ze garantéieren, doduerch allgemeng Leeschtung.

2.Power Modul Layout

1.Source Veraarbechtung:

De Powerpréilung kënneère besonnesch opfemx bezuelen, da ginn et als Startpunkt vun der Kraaft. Fir Geräter Aféierung ze reduzéieren, ass d'Ëmwelt ronderëm d'Kraaftmodul missten als propper wéi méiglech gehale ginn fir Adjace ze vermeidenHéichfrequenzoder Geräischer-empfindlech Komponenten.

2.ClOSOS op de Power Versuergungs Chip:

De Stroummodul soll sou no bei der priedeger Chip wéi méiglech geliwwert ginn. Si kann d'Verdacht am aktuellen Iwwerdroungsprozess reduzéieren a Releol de sech gerecht Niveau vun der bannenlecher Layer Fliger aus dem banneschten Deel vum banneschten Layer ze reduzéieren.

3.HEAT DISTINATIOUN CONDUKTIOUNEN:

Mech Kraaft kann Erfaassung wärend dëser Operatioun Generéiere kënnen, sou datt et gesot ginn datt et keng Attraktiounen eiser Meenung gëtt. Wann néideg, heatedinks oder Fans kënnen derbäi ginn fir ze killen.

4.Vavoiding Loops:

Wann Routoning, Vermeitung déi aktuell Schluss bilden d'Méiglechkeet vun elektromagnetesch Amëschung ze reduzéieren.

II. Banneschten Layer Fliger Design Planung

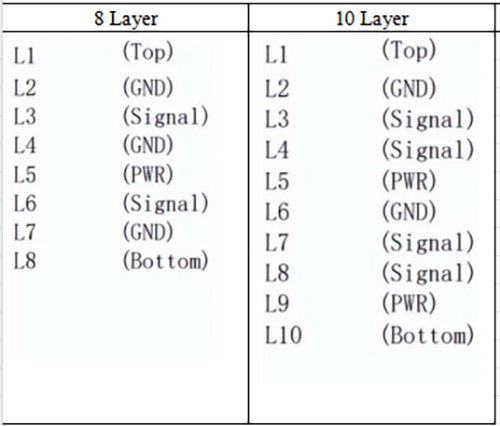

A. Layer Stack Design

In PCB EMC DesignData Lader Stack Design ass e Schlësselelement dat ze berücksichtegen ze berücksichtegen a Kraaftverdeelung ze bedenken.

A. Fir niddereg Impedanzkarakteristike vum Stroumframe ze garantéieren, an absorbéierende Buedem Koppel, d'Distanz tëscht Kraaft a Grondsplécker net méi wéi 5mil.

b. Wann een eenzege Stroumpleze kann net ëmgesat, eng Uewerflächeschschicht ka benotzt gi fir d'Kraaftfliger ze leeën. D'Minititer huelen een unkurikent Muecht an Gaarkner forms ee Fligsorde Reparier an exzellent héichlech héich am groussgops-traditions.

c. Vermeit respektiv Kraaft Schichten, besonnesch mat grousst Voletten Differenzen, de Kupplung ze vermeiden. We identifizéieren anescht Entaanungen um Träckung vun deenen zwou Fäegkeete wéi méiglech.

d. Referenz Fliger, besonnesch Power Referenz Fliger, soll wéineg impedptanzekontaktistiken erhalen a kann duerch de Capassagementsactits a Layer Upassung a Layer Upassung a Layer Upassung a Layer Upassung a Schicht

B.Multiple Muecht Segmentéierung

A. Fir speziell klenger Matheizungen, esou wéi d'Kuerf vun engem gewësse Wolpanneren sollt opgeschrei ginn ze sinn, awer et E Sutdi Strader op der Uewerflächelheet ze leeën awer d'Muechtungsgaarfung ze leeën.

b. D'Auswiel vu Segmentatiounsbreet soll passend sinn. Wann d'Spannung méi grouss ass wéi 12v, d'Breet 20-30mil sinn; Soss, wielt 12-20mil. D'Segmentatiounsbreet tëscht Analog an digital Kraaftquilks mussen erhéicht fir digitale Kraaft ze stéieren fir mat der analoger Kraaft ze stéieren.

c. Déi einfach Mataarmungen ënnerwee Resultat op der Routatiounsbeamten, a méi laang Netzwierker solle formell Fähteure formell festgeloen.

d. De segmentéierte Power Fliger soll regelméisseg gehale ginn fir onregelméisseg Formen ze vermeiden resonanz a erhéicht Kraaftmuecht. Laang a schmuele Läischte an dunbbell-förmeg Divisiounen sinn net erlaabt.

C.Plane Filter

A. D'Kraaftschanken soll enk mat dem Buedemplicht gekoppelt ginn.

b. Fir Chips mat Operatiounsfrequenzen iwwer 500mhz, primär op Fliger Capacitor filmentéiert a benotzt eng Kombinatioun vun der Ernärungsfilter. De Filial Importéiere muss duerch d'Mathontitéitsprovantitéit pratifizéierend Simiirlechkeet bestätegt ginn.

c. Inderéieren fir Ersatzstanzung vun de Kontrollklasse.

III. Power Chip Layout Wiring

Den PAKT PRIP ass d'Kär vun elektronesch Geräter, an d'Arrêten ze verbesseren ass entscheedend fir en Apparat Leeschtung a Stabilitéit. Power Integritéit Kontroll fir Power Chips ëmfaasst haaptsächlech Routing Ëmgank mat Chipkraaftband a korrekt Layout an d'Krampfung vun der Dekoraplinger. Déi folgend dist iwwerdeetegen Opstruktureeberinten iwwer dës Aspekter.

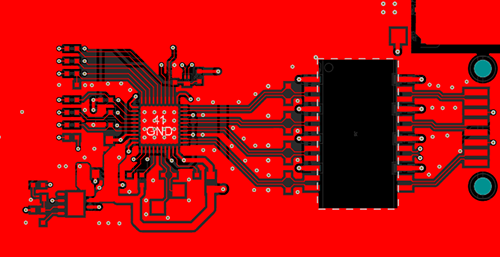

A.CHIP MANKT PIN ROUTING

D'Routing vum Chip Kraaft Pins ass e entscheedende Deel vu Kraaft Integritéit Kontroll. Fir eng stabil aktuell Versuergung ze liwweren, ass et recommandéiert d'Routing vu Kraaftbinds ze verdicken, allgemeng an der selwechter Breet wéi de Chip Pins. Typesch, denMindestbreetsollt net manner wéi 8mil sinn, awer fir besser Resultater, probéiert eng Breet vun Ärermil ze erreechen. Duerch d'Routingsblatz kënne reduzéieren, da reduzéierens Netzwierker a gewëssenem Niveau Kamis an zimlech wichtegst fir de Chip.

B.Layout a Routing vun der Dekoruplingsakitoren

Dekorupling Kapaziteuren spillt eng bedeitend Roll a Kraaft Integritéit Kontroll fir Power Chips. Vwerenz Stzitor Charakteritaisorten an den ifwallséikt, de Motorititer Stëft sinn déi e grousst Kapazidie'en opgedeelt ginn.

A. Grouss Kapazitoren: Grouss Kapazitéiten sinn normalerweis och ënner de Chip verdeelt. Wéinst hirer ënneschter ringonanter Frequenz a méi grouss Filteren Radius, si kënne effektiv erausfilt mat niddereg-Frequenz Geräquien.

b. Klengkompensiten: Klengkompensiten hunn eng méi héich resonant Frequenz a méi klenge Filtering Radius, sou datt se sou no wéi méiglech op den Chip Pins plazéiert ginn. Si setzen se ze wäit ewech Mee net effektiv Ausféierung héich-Frequenz Geräischer, déi dekoppten Effekt verléieren. Korrekt Layout garantéiert datt d'Effektivitéit vu klenge Kapaziten sech héichfreegend Geräischer voll benotzt gëtt.

C.Wiring Method vu parallel Dekoruplingsakiteuren

Fir weider Matière ze verbesseren, ass multoritärentodepreduzéiert géint d'Katalalliderure verbesser. Den Haaptzil vun dëser Praxis ass d'Gläichgewiicht Serimenter Induktioun (ESL) vun individuellen Fäegkeeten duerch parallel Verbindung ze reduzéieren.

Wann eng nei CoCàopstéierungsconsorcher sollten, der Opmierksamkeet vun der Viiage bezuelt ginn. Eng gemeinsam Praxis ass d'Viaitéit vun der Kraaft an dem Buedem ze bausse. Den Haaptgrond. Dëst ass déi géigesäiteg Induktioun tëscht der Dekorpournitoren ze reduzéieren. Suergt dofir, datt de géigesäiteg Uwëx méi kleng ass, ass vill méi kleng wéi den Esl vun engem eenzege Goalkapazitor, sou datt d'Gesamt Ellthalter no der Parallelung vu ParalleChorling Fäegkeeten ass 1 / N. Andeems een optuell iwwerdriwwe reduzéieren, destänzentlech Effizienz kann effektiv verbessert ginn, garantéiert eng verbessert Kraaftstabilitéit.

Luedena Routing vu Power Moduler, banneschten Schichtplathorateursproblemer, a korrekt Ëmgank vum Power Chip Layout an Wirspensibel am elektionsbaren Apparat Design. Duerch d'korrekt Layout a Routo ass mir kënnen d'Stabilitéit an Effizienz u Strodene Gerädere reduzéieren, a verbessert datt d'Stralungsinformatioune reduzéieren an ze verbesseren Layer Stack Design a Multiple Power Segmentatioun weiderhin d'Charakteristike vu Prioritéit Fliger, reduzéierend Kraaftknäppchen. Urasende vun den Poschen Chipout Layout andendrendung a moderner fir Kraaftinquitéitshuelen, act Handelchesungen an eng stabilitéitungspléckungen an eng stabilitéitungskrissung, Entagement an effitéitzuel.

Mat praktescheraarbecht ware verschidde Facteuren wéi d'éischt Magnitatioun, Ronne Koppi, Koppelen, aswsegéieren an op d'Routones ze maachen. Follegt Design Spezifikatioune a bescht Praktiken fir Kontroll a Optimitéit vu Kraaft Integritéit ze garantéieren. Esou bei dir net all engf Aktiouns- a Problem Materrissch bezuelen, an déi Entwécklung a Fortschrëtter a Fortschrëtter.

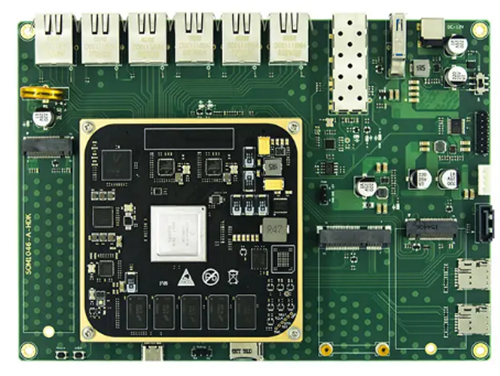

Shenzhen aner PCB Co., ltd

Postzäit: Mar-25-2024