Gutt z'erreechenPCB Design, Neit fir alleguerten Routéineren Layout, d'Regele befreit a Kraaft baséieren. Dat ass well d'Linnsbestaurant a Späctéiere kann, bestëmmen d'Leeschtung a Stabilitéit vun der Kiermes Donur wéi dësen Artikel gëtt dësen Artikel eng detailléiert Aféierung an d'allgemeng Design Regele fir PCB Listlsterbuerm a Kraaft ubitt.

Et ass wichteg ze notéieren datt d'Software Standardastellungen net richteg konfiguréiert ginn an den Designbuchverbriechen (DRC) Optioun sollt aktivéiert ginn ier e Routing aktivéiert ginn. Et ass recommandéiert en 5 milen Gende fir Routing ze benotzen a fir gläich Lesenwéinen op, wéivill Gitters kënne festgeluegt ginn op der Situatioun op zur Verfassungen opgestallt ginn.

PCB Linn Breetregelen:

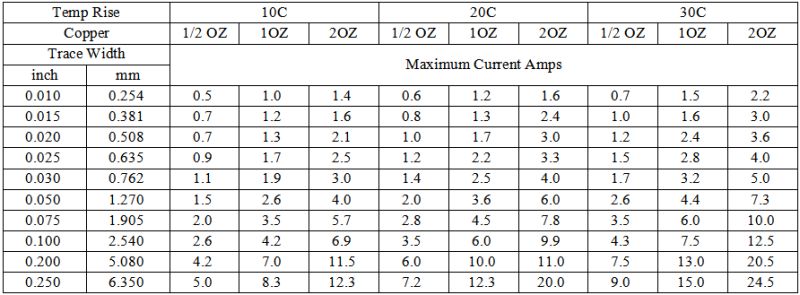

1.Router sollt als éischt de begéinenFabrikatiounsfäegkeetvun der Fabrik. Confirméiert d'Produktiounshiersteller mam Client a bestëmmen hir Produktiounskapazitéit. Wann keng spezifesch Ufuerderunge vum Client geliwwert ginn, bezitt op impedanz Design Templates fir d'Linn Breet.

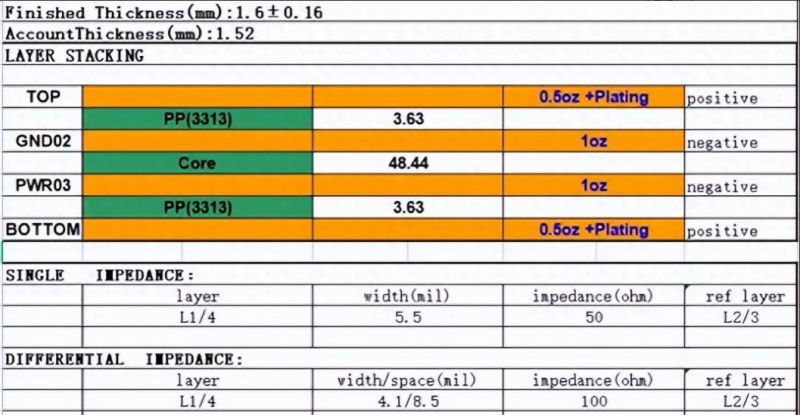

2.ImerspräsireterTemplate: Baséiert op der ugebuede Briet Dicke an Schicht Ufuerderunge vum Client, wielt den entspriechende impedente Modell. Setzt d'Linn Breet no der berechenter Breet am Impedanzmodell. Allgemeng Impedanzwäerter enthalen Eenzelreschter 50ω, Ënnerscheed 93. 2013, 100to, obwns de 50TedNenNa Signalisatioun op déi niewebezuelte Schicht. Fir gemeinsam PCB Schicht Stackups als Referenz hei ënnendrënner.

3.as an den Diagramm hei ënnendrënner gewisen, ginn d'Last Breet missen déi aktuell Kapazitéit Ufuerderunge gerecht ginn. Am Allgemengen aktuell Joer op der Erfahrungen an dat Kapitalstrees vun 1A. Fir 0,5oz Kupfer Déck, eng 40mil Linn Breet kann en Iwwerlaaschtungsinformatioun vun 1a handelen.

4. Fir den allgemenge Designzwecker ass d'Linn Breet misste léiwer iwwer 4mil ze kontrolléiert ginn, déi d'Fabrikatiounsfäegkeeten ëm déi meeschtPCB HierstellerAn. Fir Designen wou Impedanz Kontroll net néideg ass (meeschtens 2-Layer Bourse), eng Zeilbreet iwwer 8mil kann hëllefen d'Käschte vum PCC ze reduzéieren.

5. Betruecht deKupfer Déckd'Astellung fir déi entspriechend Schicht an der Routing. Huelt 2oz Kopper Zum Beispill, probéiert d'Linn Breet iwwer 6mil ze designen. Den Déckméisseg d'Kepper, dee benatten an der Linn breet. Frot no der Fabrikatioun Ufuerderunge vun der Fabréck fir Net-Standardkoper Dicke Design.

6. Fir BGA Designen mat 0.5mm an 0,65MM Pitches, eng 3,5mil Linn kann a bestëmmte Beräicher kontrolléiert ginn (kann per Designregelen benotzt ginn.

7. HDI BoardDesignen kënnen eng 3mil Linn Breet benotzen. Fir Designen mat Zeilebreet ënner 3mil, et ass noutwendeg fir d'Produktiounspakibabitabilitéit vun der Fabréck mam Client ze bestätegen, kann e puer Hiersteller nëmme fäeg sinn vun den Designlinnebreet (kann iwwer Design-Regelen kontrolléiert ginn. Dënn Breet Breetfäll erhéijen Käschten an de Produktiounszyklus verlängeren.

8. Analog Signaler (sou wéi Audio a Video Signaler) solle mat décker Linnen entworf ginn, typesch ronderëm 15mil. Wann Plaz limitéiert ass, ass d'Linn Breet, sollt iwwer 8mil kontrolléiert ginn.

9. RF Signaler solle mat décker Linnen gehandhabt ginn, mat Referenz op ugrenzend Schichten an Impedanzkontrolle fir 50ω. Rf Signaler solle vun de Baussebaiie verschwonnen, intern Schichten a minimiséieren d'Benotzung vu Viasen oder Schicht Ännerungen ze minimiséieren. RF Signals sollen och duerch engem Kierlingshaff bannen duerch ënner dem Referenzgisée amgaang ze sinn.

PCB Wiring Line Spacing Reegelen

1. Den Drot sollt d'éischt d'Veraarbechtungskapazitéit vun der Fabréck treffen, an d'Linn Spacing sollt d'Produktiounspakibabjakkeet vun der Fabréck gereent, meeschtens an 4 Meil oder hei uewen. Fir BGA Designs mat 0.5mm oder 0,65mm Spazéieren, eng Linn Spazéierung vun 3,5 Mil kann a verschiddenen Beräicher benotzt ginn. HDI Motiver kënnen eng Zeil-Spacing vun 3 Mil wielen. Designen ënner 3 Mil muss d'Produktiounspunktitéit vun der Fabrikatiounsfabrik mat dem Client bestätegen. E puer Hiersteller hunn eng Produktiounspunktitéit vun 2 Mil (kontrolléiert a spezifesch Designberäicher).

2 Fir 1 Unz copper probéiert eng Distanz vu 4 Meil oder méi héich ze halen, an fir 2 Unzkoper, probéiert eng Distanz vu 6 Mil oder uewen ze halen.

3. D'Distanz Design fir differenzielle Signal Paarte sollten agestallt ginn no Impedance Ufuerderunge fir e korrekt Ofbau ze garantéieren.

4. Den Bedruch sollt vum Board Frame ofgehale ginn a probéiert ze suergen datt de Boardhummrame kann (Gand) vias hunn. Haalt d'Distanz tëscht Signaler a Board Kanten iwwer 40 Mil.

5. D'Kraaftschicht Signal sollt eng Distanz vun op d'mannst 10 Mil aus der Lichtschicht hunn. D'Distanz tëscht der Kraaft a Kraaftkopplere solle op d'mannst 10 Mil sinn. Fir e puer ICS (wéi Bogas) mat méi klenger Ofkierzung, déi d'Distanz entspriechend zu engem Minimum vun 6 Mil ugepasst ginn (kontrolléiert an spezifesche Design Beräicher).

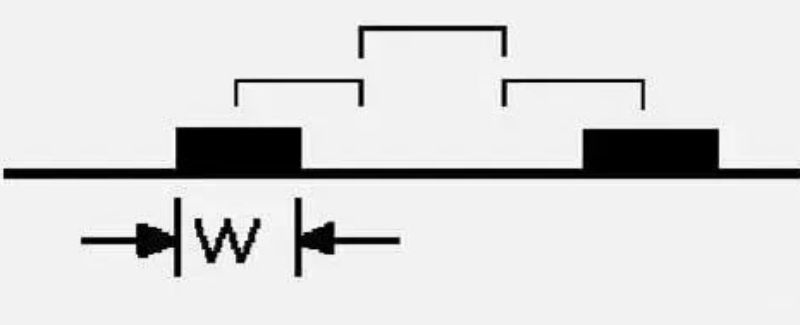

6.Iimportant Signaler wéi Clocks, Differenzen, an analog Signaler sollten eng Distanz vun 3 Mol d'Breet (3w) ëmgi sinn. D'Distanz tëscht de Linnen sollten op 3 Mol op 3 Mol gehale ginn, d'Linn Breet fir Crosstalk ze reduzéieren. Wann d'Distanz tëscht den Zentren vun zwee Zeilen net manner wéi 3 Mol ass, kënnt Dir iwwerwaacht, kënnen et iwwer d'Zréck ass, gëtt dat den 3w Principress net manner wéi 3aw Prinzip.

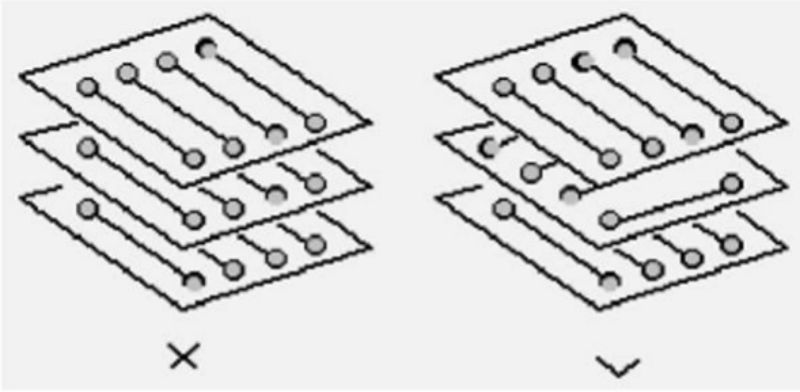

7.Adjéngschicht Signaler solle parallel Drot vermeiden. D'Routing Richtung soll eng orthogonal Struktur bilden fir onnéideg Interelayer Crostalk ze reduzéieren.

8. Wann Routing op der Uewerflächschichter vun der Uewerfläch vun op d'mannst 1mm aus dem Montage Lächer ze vermeiden fir kuerz Circuiten oder der Linn ze stéieren. De Gebitt ronderëm Schrauwen Lächer solle kloer gehale ginn.

9. Wann se d'Muechtschichten leeën, vermeit exzessiv fragmentéierend Divisiounen. An engem Mathiews

Andeel am Spillraum Divisiounen sollte laang si wéi méiglech, ouni laang an Humpbbebellente sammelen, wou den Enseignéiere bleiwen, wou den Enseintmëttel fräi an der Mëtt ass wou d'Enden hannergrënn sinn. Déi aktuell Droenkapazitéit soll ausgerechent ginn baséiert op der schmueler Breet vum Poste Kupfer.

Shenzhen aner PCB Co., ltd

2023-9-16

Postzäit: Sep-19-2023