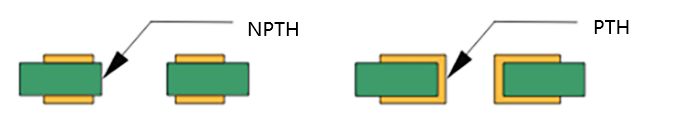

D'Lächer opPchebokann duerch Lächer duerch Lächer klasséiert ginn (pth) an net duerch Lächer (NPT) baséiert op ob se elektresch Verbindunge hunn.

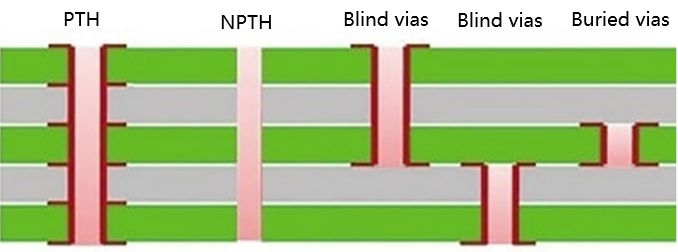

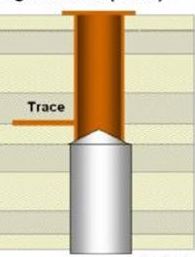

An der Bléck gepickt duerch d'Lach (PT) bezitt sech op e Lach mat engem Juket mat senge Wänn, déi d'Elektresch Konformatiounen an der Innere Schicht erreechen, oder béid vun engem PCB. Seng Gréisst gëtt vun der Gréisst vum gebuerene Lach an der Dicke vun der platter Schicht bestëmmt.

Net vun de Lächer (nph) sinn, sinn d'Lächer déi an der elektresch Verbindung vun engem PCB-Cours mat enger Spass gespaalen. De Schicht kann duerch d'Lach duerch de PCB Pëllen duerchdroe ginn, hu Lächer méi wéi duerch klengt Lach verbrannt ginn, a blann Vidy via Lach.

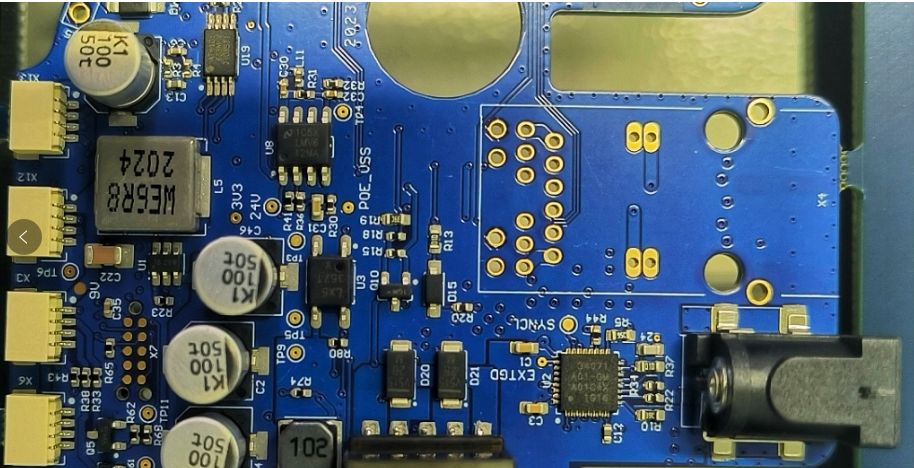

Duerch-Lächer penetréieren de ganze PCB a ka fir intern Verbindunge benotzt ginn an / oder Positioun vun Komponenten. Ënnert hinnen, d'Lächer déi benotzt gi fir Fixéierung an / oder elektresch Verbindungen mat Kompleideren Ternalen (Dréit an Dréit) op de PCB CONGNS VERSTÄNNEST HOLDEN. Plënnert duerch-Lächer fir intern Schichtenverbindunge benotzt, awer ouni Montage Komponent Leads oder aner Verstäerkungsmaterialien genannt ginn iwwer Lächer. An der Basis sidd haaptsächlech Zwëschenzäiten fir Billen duerch kleng Sichen: Et ass eng Ouverture duerch de Booupitéituzungsfehler ze schafen; normalichte, an am Insamayen. D 'Ofgrenzung vum Brandoequipe Deen aneren ass op déi strukturell Integritéit an d'Positioun vun der Komponent vun der Komponent Installatioun am Board.

Bindeg Vuelre a verbunn via benotzt ginn wäit an der Dichtungsnessinknoden (HDI) Technologie vum HDI PCB, meeschtens an HIG Laybe PCB. Blann Vias verbënnt normalerweis déi éischt Schicht un déi zweet Schicht. An e puer Designen, blann Vase kann och an der drëtter Layer an der drëtter Schicht verbonnen. Andeems Dir e bësse komesch verbreete viziéiert, méi Verbindungen a méi héich Circuitverbraucher Verlaangen, déi vum HDI erreecht ginn. Dëst erlaabt eng erhéicht Schichtstenser zu méi klenge Apparater ze verbesseren beim Ofdreiwung. Verstoppt Vias hëllefen Circuit Boards Liichtgewiicht a kompakt. Blann an begruewen iwwer Designen ginn allgemeng an komplexen Design, Liichtgewiicht, an héich Käschte elektresch Produkt wéiSmartphones, Pëllen, anmedizinesch Geräter.

Big Vauiginn geformt andeems d'Déift vun der Drambieren oder Laser Abéierung kontrolléiert. Déi lescht ass de Moment déi méi gemeinsam Method. De Stacking vu Via Lächer gëtt duerch sequenziell Schicht geformt. Deen entstinn iwwer Holes kënne gehat ginn oder bedeiten, addéiere zousätzlech Fabriageatioun an Testings ze fonteren.

No der Saach an d'Funktioun vun den Lächer, kënne se klassifizéieren als:

Iwwer Lächer:

Si sinn minesaliséiert Lächer gemaach fir elektresch Benotzerfuerhëllefen op e PCB ze erreechen op e PCBB, awer net fir den Zweck vun der Membersoun.

PS: iwwer Hoeder kënne kollm an duerch-Lach kolltten, brujienz a blannsch, d 'uewen, wou d'L Lach fir am Pauch ugeet.

Komponent Lächer:

Si si fir d'Estellung scho gespléckt anektroeschiellen Ploaarpolitenz ze befestegt ginn an esou wéi och fir en elektresch Lager tëscht verschiddene leitgeschichtene gelooss ginn. Beweiser Hellelen sinn traditionaliséiert ofgebaut, a kënnen och z'ënn esou weisen Zougang fir de Projeten fir Vëlospunkt.

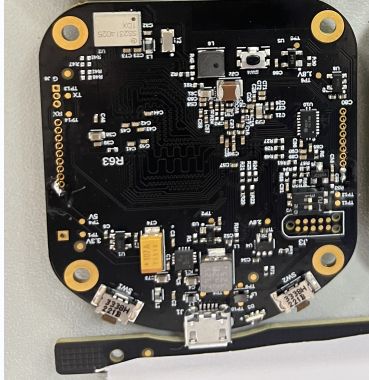

Montéierung Lächer:

Si si méi grouss Lächer um PCB benotzt fir de PCB an eng Casing oder aner Support Struktur ze sécheren.

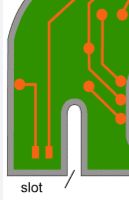

Slot Lächer:

Si ginn entweder geformt andeems se automatesch eenzel Lächer kombinéiert oder per Millengruppen am Buerprogramm vun der Maschinn. Si ginn allgemeng als Montéierungspunkten fir Strohlprizs benotzt, sou wéi déi oval-förmlech Pins vun engem Socket.

Backdrill Lächer:

Si si liicht méi déif Lächer gedronk a plazéiert Lächer op de PCB fir den Hebe ze isoléieren a Signal Reflexioun beim Transmissioun reduzéieren.

Followers sinn e puer axiliär Lächer déi PCBaboranten an der benotzenPCB Fabrikatiounsprozessdatt PCB Design Ingenieuren solle vertraut sinn:

● Loschte Lächer sinn dräi oder véier Lächer uewen an ënnen um PCB. Aner Lächer op de Board ginn ausgeriicht mat dëse Lächer als Referenzpunkt fir Positionéierungspäicher a fixéieren. Och bekannt als Zil Lächer oder Zilpositiounsauspositioun Lächer, si gi mat engem Zilhachmaschinn produzéiert (optesch Punch Maschinn oder X-Raying Maschinn a benotzt.)

●Banneschten Schicht AusrichtungLächer sinn e puer Lächer um Rand vum Multilayer Board, benotztent fir ze feststellen ob et iergendee Departement am Badilayer am Bord ass an der Grafik vum Board. Dëst bestëmmt ob de Buerprogramm muss ugepasst ginn.

● Gitt Holes sinn eng Rei vu klenge Lächer op enger eenzeger Säit vum Bordinformatioun fir e puer Produktiounsinformatioun, sou wéi Produktmodell, Veraarbechtungsmaschinn am Moment.

● Genëllegen Doheem sinn e puer Lächer vu verschidde Stapp iwwer um Randeckeren, well de Réiermëschung vum Vëréngner ass während der Spuerrächtert? Do kommen och vill Saache benotzen aner Technologien zu dësem Zweck.

● Ausbrochbunne ginn Platten Platten benotzt fir PCB analyséieren an Analyse fir d'Qualitéit vun de Lächer ze reflektéieren.

● Dämmerungstext Lächer gi gepickt Lächer fir déi ugewannt fir den impedentanz vum PCB ze testen.

● Analyse Lächer sinn normalerweis net geplënnert Lächer déi benotzt gi fir zréckbezuelt zréck ze positionéiert ginn, a ginn dacks an der Schold oder Imaging Propositioun benotzt.

● Tooling Lächer sinn allgemeng net-plats Lächer fir verbonne Prozesser benotzt.

● Rivett Lächer sinn net gepickt Lächer fir d'Fehler tëscht all Schutzmaterial a Bliederblat a multilayer Leader Lamains ze fixéieren. D'Reim Positioun muss duerch Droë gedrazt ginn fir Bubbrénge vun där Positioun ze bleiwen, déi d'Boardulakuatioun verurs kéinte mat spéideren Prozesser verursaachen.

Geschriwwen vum Anke PCB

Postzäit: Jun-15-2023